What is Clock Data Recovery and How Does it Work?

Clock data recovery is key in digital communications. It helps pull timing info from a data stream itself. This makes it possible to know the timing of the data without needing a separate clock signal.

This process is vital for fast data transfer. It ensures the signal stays strong. In data transmission, getting the clock signal right is essential for reliable data transfer.

A closely related example also appears in rescue data recovery services, where many of the same practical issues show up in a slightly different way.

High-speed serial links use data signal changes to find timing. The design of clocking circuits is linked to this timing recovery. Clock recovery is very important for digital systems’ performance and reliability.

It keeps the signal strong and is used in many areas. This includes fast serial communications, optical networks, and wireless systems.

We will look into clock data recovery‘s basics, uses, and challenges. We’ll cover different methods like traditional CRCs and oversampled CRCs. We’ll also talk about keeping PLLs and DLLs stable for signal integrity.

Understanding clock data recovery helps us see its role in digital communications. It’s key for fast data transfer and maintaining signal quality.

Understanding Clock Data Recovery: Basic Principles

Clock data recovery is key in digital communications. It helps pull timing info from a data stream. This lets us figure out the timing of data without a separate clock signal.

At the receiving end, clock recovery is vital for high-speed data streams like Ethernet. This is because there’s no specific clock info given.

A phase-locked loop (PLL) is used to align with incoming data. This extracts a proper clock signal. The 64B/66B encoding scheme helps by ensuring enough data transitions.

This reduces consecutive identical data symbols. The clock frequency must be close to the incoming data’s. A Voltage Controlled Oscillator (VCO) is used for frequency detection.

The training sequence helps the receiver lock onto the data stream’s frequency. In Clock Data Recovery (CDR), the recovered clock is used to re-time the data signals. For CDR to work, the receiver’s frequency must match the transmitter’s.

Continuous phase alignment is needed. This adjusts the clock based on data stream variations.

| CDR Component | Description |

|---|---|

| Phase Detector | Detects phase differences between the incoming data and the recovered clock |

| Loop Filter | Filters the output of the phase detector to control the VCO |

| Voltage-Controlled Oscillator (VCO) | Generates a clock signal based on the control voltage from the loop filter |

The Importance of Synchronisation in Digital Communications

In digital communications, keeping data in sync is key. Clock data recovery systems help by pulling out the clock signal from data. This is vital for cutting down jitter tolerance and making sure data gets through right.

Studies show clock recovery is a big part of many tests. For example, data recovery best practices stress its role in keeping data safe. Key points about clock data recovery include:

- Loop bandwidths: usually between 1 to 10 MHz

- Jitter tolerance: better with wider loop bandwidth, but adds noise

- Clock recovery methods: mainly used for NRZ data formats, with PLL being the top choice

In summary, synchronisation is very important in digital communications. Clock data recovery systems and jitter tolerance are key to this. They help ensure data is sent reliably and keeps digital communications strong.

| Parameter | Description |

|---|---|

| Loop Bandwidth | Typically ranges from 1 to 10 MHz |

| Jitter Tolerance | Improved with a wide loop bandwidth, but increases noise |

| Clock Recovery Method | Applied to NRZ data formats, with the most prevalent architecture being based on a Phase Lock Loop (PLL) |

Components of a Clock Data Recovery System

A clock data recovery system has several important parts. These include a phase detector, loop filter, voltage-controlled oscillator, and decision circuit. Together, they help to accurately data re-time and lower bit error rate.

The phase detector is key in matching the receive clock’s phase and frequency with the data. This is very important in high-speed systems. Here, a low bit error rate is vital for good performance.

The loop filter and voltage-controlled oscillator work together. They control the clock’s frequency and phase. The decision circuit then uses this clock to accurately data re-time the incoming data. This helps to keep bit error rate low.

When designing a clock data recovery system, controlling the clock’s phase and frequency is important. Also, the effects of jitter and phase noise on performance must be considered. By choosing and designing these components carefully, designers can reduce bit error rate and ensure accurate data re-timing.

| Component | Description |

|---|---|

| Phase Detector | Aligns receive clock’s phase and frequency with incoming data transitions |

| Loop Filter | Controls frequency and phase of recovered clock |

| Voltage-Controlled Oscillator | Generates clock signal based on loop filter output |

| Decision Circuit | Re-times incoming data using recovered clock |

How Clock Data Recovery Works in Practice

Clock data recovery is key in data transmission. It helps pull out clock information from data signals. It’s used in many fields like telecommunications, data centers, and cars.

The system has parts like a phase detector and a voltage-controlled oscillator. These help get the clock signal right.

This process is vital for high-speed data. It makes sure the clock signal is correct. This is important because the clock is hidden in the data stream.

Clock recovery syncs the receiver’s clock with the sender’s. A phase-locked loop (PLL) does this. It adjusts the receiver’s clock to match the sender’s.

It’s important to consider the clock difference and noise effects. The clock difference can be up to 50 ppm. Noise and jitter can also affect the clock signal.

Designing a good clock recovery system is complex. It needs to handle clock frequency, data rate, and noise levels. Knowing how it works helps make data transmission faster and more reliable.

Common CDR Architectures and Implementations

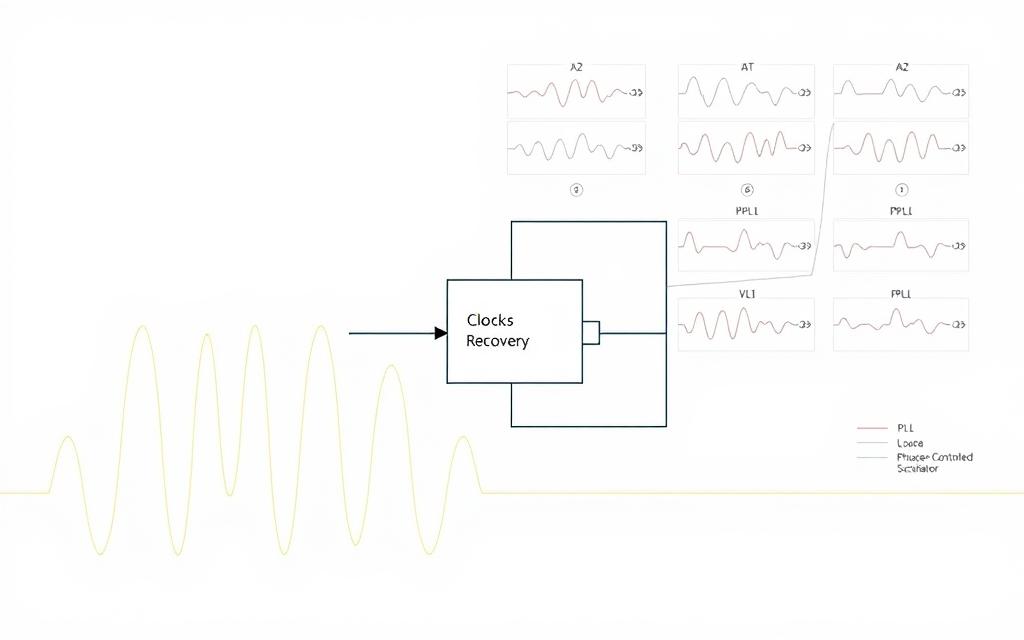

In digital communications, Clock Data Recovery (CDR) systems are key for reliable data transfer. The phase-locked loop (PLL) is a common method for clock recovery. PLL-based CDR designs can be analog or digital, depending on whether they use a reference clock.

CDR architectures vary, including feedback phase tracking, oversampling, and phase alignment without feedback. The right architecture depends on the application and system needs. For instance, in high-speed serial communications, a PLL-based CDR with a reference clock is often used for precise clock recovery.

The advantages and disadvantages of each approach are as follows:

- Linear CDR systems: offer high accuracy and stability, but can be complex and power-hungry.

- Binary CDR systems: are simpler and more power-efficient, but may have lower accuracy and stability.

- Hybrid approaches: combine the benefits of linear and binary systems, providing a balance between accuracy, stability, and power consumption.

For more information on CDR architectures and implementations, visit Clock and Data Recovery structures and types of CDRs.

The following table summarizes the key characteristics of different CDR architectures:

| Architecture | Advantages | Disadvantages |

|---|---|---|

| Linear CDR | High accuracy and stability | Complex and power-hungry |

| Binary CDR | Simple and power-efficient | Lower accuracy and stability |

| Hybrid CDR | Balance between accuracy, stability, and power consumption | More complex than binary CDR |

Challenges in Clock Data Recovery Design

Clock data recovery systems face many challenges, like jitter tolerance and bit error rate. At high speeds, these systems must match the data rate. For example, a 10 Gb/s data rate needs a clock frequency of 10 GHz.

The clock period for such a data rate is 100 ps. This means the system must keep output jitter low. High-speed applications require this to ensure reliable data transmission.

A major challenge is the skew effect, which gets worse at high speeds. To tackle this, designers use techniques like the Hogge phase detector. It helps detect edges and produces linear pulses, avoiding false locks.

For more details on clock data recovery systems, check out clock data recovery research.

Some key challenges in clock data recovery design include:

- Minimizing output jitter to reduce retimed data jitter

- Addressing the skew effect at high speeds

- Improving jitter tolerance to ensure reliable data transmission

In conclusion, clock data recovery systems are vital for reliable data transmission. Overcoming design challenges is key to better jitter tolerance and lower bit error rates.

Applications of Clock Data Recovery

Clock data recovery is key in many digital fields like serial communications, optical networks, and wireless systems. It aims to pull out the clock signal from data streams and sync the data. This makes sure data is sent reliably, cutting down on errors.

In fast serial communications, it’s vital to get the clock signal right. This is true for Ethernet, where data travels without a clock signal. The recovered clock helps sync the data, lowering error rates and boosting system performance.

High-Speed Serial Communications

In optical networks, clock data recovery is essential. It extracts the clock signal from optical signals and syncs the data. This is critical in long-distance optical fiber communications, where signals can weaken.

Optical Networks

In wireless systems, clock data recovery is also vital. It pulls out the clock signal from wireless signals and syncs the data. This is important in WLANs, where signals can face interference.

Using clock data recovery brings many benefits. It improves system performance, lowers error rates, and increases reliability. By syncing data with the system’s clock, it reduces errors and boosts performance. It also makes systems more reliable by providing a stable clock signal.

Performance Metrics and Testing Methods

Performance metrics and testing methods are key for clock recovery systems. They ensure data transmission is reliable and accurate. Jitter tolerance, bit error rate testing, and phase noise analysis are important metrics.

Jitter tolerance shows how well a system handles timing variations. This is vital in high-speed serial links. Even small timing changes can cause data errors. Bit error rate testing counts errors during data transmission, showing system performance.

Key Performance Metrics

- Jitter tolerance: measures the system’s ability to tolerate variations in signal edge timing

- Bit error rate testing: measures the number of errors that occur during data transmission

- Phase noise analysis: measures the random fluctuations in the phase of a signal

These metrics are vital for clock recovery system performance. They are more important in high-speed data transmission. By understanding these metrics and using the right testing methods, developers can improve their systems’ performance and reliability.

Advanced CDR Techniques and Innovations

Recent breakthroughs in clock data recovery (CDR) have boosted digital communications systems’ performance and reliability. The use of phase-locked loop (PLL) architectures is a key innovation. It allows for more precise and efficient clock recovery. This leads to faster data transfer rates and better signal quality.

Advanced CDR techniques also enhance the timing margin of digital communications links. For instance, a second-order CDR with precise frequency estimation can achieve zero lock time in burst mode receivers. This is vital in high-speed systems, where small timing errors can cause big data issues.

Some key features of advanced CDR techniques include:

- Improved frequency estimation and tracking

- Increased timing margin and reduced jitter

- Enhanced signal integrity and data transfer rates

- Support for high-speed digital communications protocols

New CDR architectures and technologies have made these advancements possible. Hybrid analog-digital quarter-rate clock and data recovery circuits are among them. These circuits offer high tracking ranges and sub-picosecond phase resolution. They’re perfect for high-speed digital communications systems.

The use of advanced CDR techniques and innovations is essential for high-speed digital communications systems. By using these advancements, system designers can create more efficient, reliable, and high-performance digital communications links. This is vital for applications like high-speed data centers and wireless communication networks, all relying on digital communications and phase-locked loop technologies.

Best Practices for CDR Implementation

When setting up clock data recovery systems, it’s key to think about several design factors. This ensures the system can accurately and reliably re-time data. One important factor is jitter tolerance, which is how well a system handles clock frequency changes. Designers need to balance jitter tolerance with other system aspects like bit error rate and power use.

Some key things to consider for CDR implementation include:

- Choosing the right clock data recovery architecture and technology for your needs

- Making sure the system has enough jitter tolerance for reliable data transmission

- Adjusting system parameters, like loop filter bandwidth and gain, to find the best balance

By following these best practices and carefully thinking about design factors, developers can make high-performance clock data recovery systems. These systems meet the needs of today’s data communication apps.

Also, knowing the stats and standards for jitter measurement, like those from SONET, helps designers. This knowledge is key for optimizing systems for specific data rates and uses.

| Data Rate | f0 | f1 | f2 | f3 | ft |

|---|---|---|---|---|---|

| 155 Mb | 10 Hz | 30 Hz | 300 Hz | 6.5 kHz | 65 kHz |

| 622 Mb | 10 Hz | 30 Hz | 300 Hz | 25 kHz | 250 kHz |

| 2.488 Gb | 10 Hz | 600 Hz | 6,000 Hz | 100 kHz | 1,000 kHz |

By thinking about these factors and following best practices for CDR implementation, developers can make high-performance systems. These systems have the best jitter tolerance and ensure reliable data transmission for modern data communication apps.

Future Trends in Clock Data Recovery Technology

The clock data recovery market is set to boom, with a forecasted size of USD 14.64 billion by 2032. This growth is at a compound annual growth rate (CAGR) of 13.26%. The main driver is the need for faster data transmission, which 5G networks will bring.

Dual-channel systems are becoming more popular, expected to lead the market. The push for bit error rate and data re-timing improvements is also fueling innovation in clock data recovery.

Several areas are driving the clock data recovery market’s growth. These include:

- Consumer devices, such as smartphones and tablets

- Automotive systems, like Advanced Driver Assistance Systems (ADAS)

- Data centers, with more AI and ML use

North America is expected to lead the market due to its strong R&D and growing economy. Yet, the lack of uniform regulations across regions is a challenge to growth.

| Market Size (2023) | Projected Market Size (2032) | CAGR (2024-2032) |

|---|---|---|

| USD 4.77 billion | USD 14.64 billion | 13.26% |

Conclusion

The digital world is always changing, and clock recovery technology is key to it. It’s vital for fast data transfer in many areas. This includes high-speed serial communications, optical networks, and wireless systems.

Knowing how clock data recovery works is essential. It helps engineers make designs that work well. This is important for fast and reliable digital connections.

The need for new clock recovery solutions is growing. Keeping up with the latest in this field is important. It helps professionals lead in digital communications.

The future of clock data recovery looks bright. Those who understand it well will help shape the digital world. They will be ready for the challenges ahead.

FAQ

What is clock data recovery and how does it work?

Clock data recovery (CDR) is a method used in digital communications. It makes sure the receiver’s clock matches the sender’s data signal. This is key for accurate data transfer and lower error rates.

What are the basic principles of clock data recovery?

CDR uses a phase-locked loop (PLL) to get the clock signal from the data stream. It includes a phase detector, loop filter, and a voltage-controlled oscillator. These work together to align the data and reduce jitter.

Why is synchronisation important in digital communications?

Synchronisation is vital for digital communications. It lets the receiver accurately read the data stream. CDR ensures this by matching the receiver’s clock with the sender’s, reducing errors.

What are the key components of a clock data recovery system?

A CDR system has a phase detector, loop filter, voltage-controlled oscillator, and decision circuit. Together, they extract the clock signal and re-time the data to lower error rates.

How does clock data recovery work in practice?

CDR is used in many fields like telecommunications and automotive systems. It tackles high-speed data challenges by ensuring accurate data timing and improving digital communication reliability.

What are the common CDR architectures and implementations?

Common CDR architectures include linear, binary, and hybrid types. Each has its own benefits and drawbacks, fitting different needs based on speed, jitter, and power use.

What are the key challenges in clock data recovery design?

Designing CDR systems faces challenges like managing jitter and achieving low error rates. They must overcome these to ensure reliable data transfer despite system impairments.

Where are clock data recovery systems used?

CDR is used in many areas, like high-speed serial communications and wireless systems. It’s key for precise data transfer and error reduction in these fields.

How are CDR systems tested and evaluated?

CDR system performance is checked with tests like jitter tolerance and bit error rate testing. These ensure the systems’ reliability and accuracy in clock recovery and data re-timing.

What are the latest advancements in clock data recovery technology?

New research in CDR technology brings new architectures and techniques. These aim to enhance performance, reliability, and flexibility, opening up new applications and use cases.

What are the best practices for implementing clock data recovery systems?

Effective CDR implementation needs careful design and robust troubleshooting. Best practices help ensure systems operate accurately, reducing jitter and errors.

What are the future trends in clock data recovery technology?

The future of CDR technology looks bright, with ongoing advancements. New architectures and technologies will improve performance and reliability, enabling new applications and driving digital communication evolution.